Memristor-MOS hybrid circuit redundant multiplier

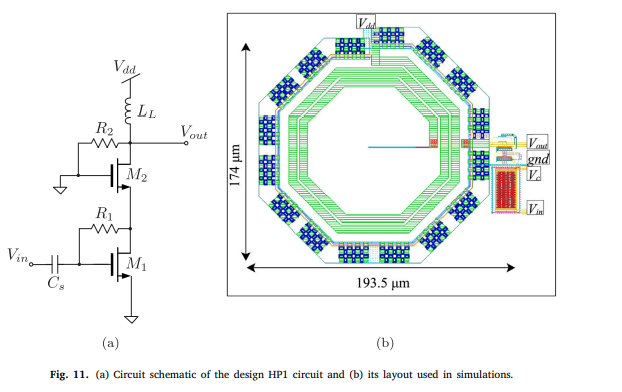

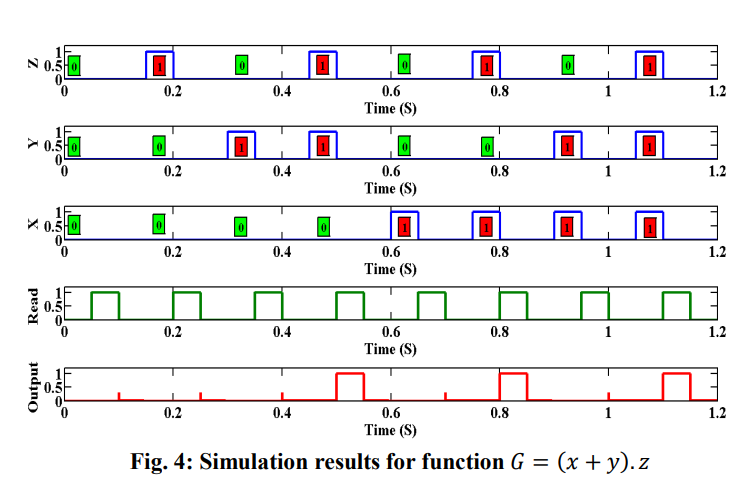

This paper introduces a step forward towards memristor-MOS hybrid circuit to achieve any combinational function. The proposed design is based on reducing the area by replacing the complete pull-down network with just one memristor and one comparator. The concept is then verified using an example of a simple function. Also, a proposed architecture for memristor based redundant multiplier circuit is introduced and verified using the SPICE simulation. Therefore, any redundant functions can be implemented using the same concept. © 2014 IEEE.